When we first started learning FPGAs, we generally downloaded the compiled .sof file (for Altera devices) to the FPGA through JTAG, but we will find that after we repower the FPGA, we gave The program it downloaded has been lost. If we still want the FPGA to run the last function, we must download the program again. This problem occurs because our program does not exist in the FPGA external configuration chip, only the internal SRAM of the FPGA.

In order to solve this problem and make our FPGA re-powered without losing the previously downloaded program, we can convert the .sof file into a .jic file and then download it to the FPGA via JTAG to solve this problem.

Let's talk about the steps to convert a .sof file to a .jic file:

1. Open the project that was compiled and produced the .sof file;

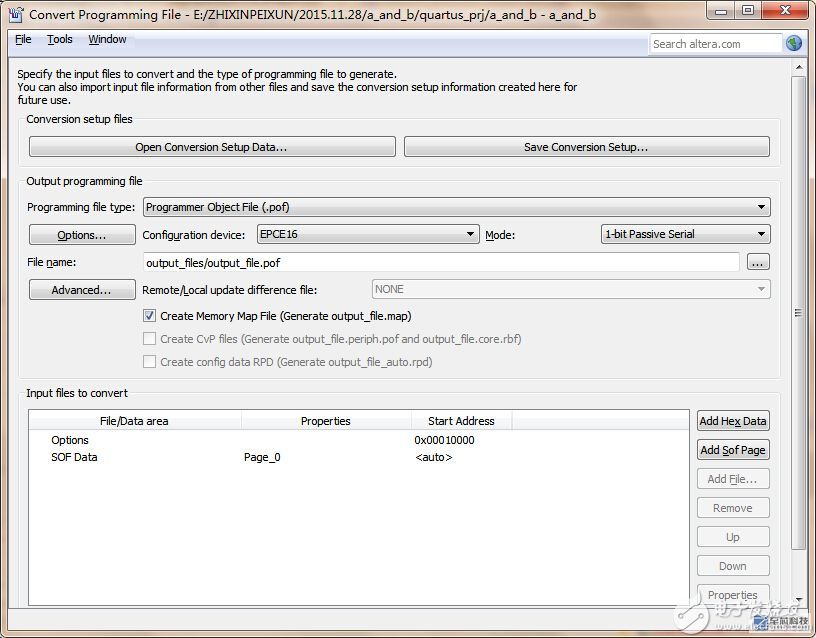

2. Click the Convert Programming Files... command under the File menu. The following interface appears;

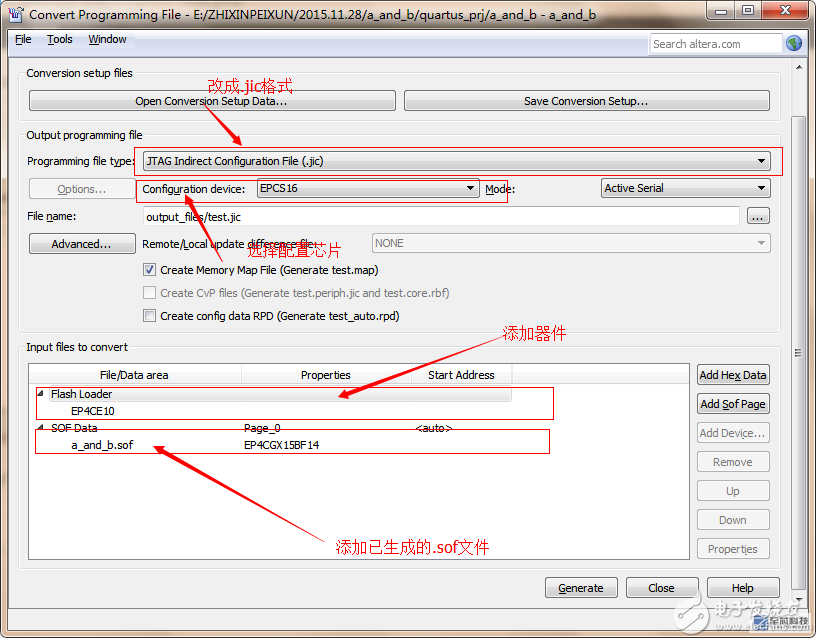

3, refer to the following figure to modify the configuration, modify the click to generate;

4, after the generation, in the download, just add the generated. Jic file on it.

Motor Three-Phase A.C Induction,Ac Motor Electric Motor Induction Motor,Electric Motor Centrifugal Pump,Electric Motor Centrifugal Switch Gear

Ningbo Zhenhai Rongda Electrical Appliance Co., Ltd. , https://www.centrifugalswitch.com