With the development of FPGA technology, the combination of digital communication technology and FPGA reflects a trend in the development of modern digital communication systems. In order to make the high-speed communication system more compact, lower cost, reduce power consumption, and especially improve the reliability of the device, QPSK digital modulation technology can be used to achieve high spectral utilization, good spectral characteristics, and strong anti-interference performance. Fast transfer rate and other features. Using verilog to write the QPSK modem code and ISE's own IP CORE on the Xilinx FPGA platform, the results show that the system can fully realize the modulation and demodulation function, and has the advantages of high integration and software upgrade.

Four-phase absolute phase shift keying (QPSK) technology is widely used in digital communication systems due to its strong anti-interference performance, good error performance and high spectrum utilization. With the advent of very large scale integrated circuits, FPGAs have become more and more widely used in digital communication systems. A variety of methods based on FPGA to implement QPSK have been proposed. In this paper, direct digital frequency synthesis (DDS) is realized based on FPGA. Phase modulation is realized by controlling the output phase of DDS signal (carrier signal). Except DA conversion, other processes can be realized by FPGA. The QPSK modulated signal is a signal that suppresses the carrier. The reference carrier cannot be extracted directly by a conventional phase-locked loop or narrow-band filter, but it is different from some continuous phase-modulated signals. The carrier phase change can only take a finite number of discrete values. The phase information of the reference carrier is implied. Therefore, the nonlinearity processing can be used to eliminate the modulation information in the signal, generate a component having a certain relationship with the phase of the original carrier, and then purify the signal to recover the suppressed carrier signal, thereby completing the coherent demodulation of the signal. The QPSK modem designed in this paper has the characteristics of small size, low power consumption, high integration, strong software portability and strong interference interference, which is in line with the future design of communication technology.

1. The basic principle of QPSK modulation

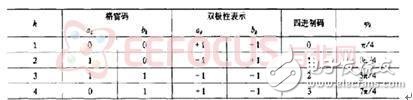

Four-phase absolute phase shift keying QPSK is a special case of MPSK that uses four different phases of the carrier to characterize digital information. Since each carrier phase represents two bits of information, each quaternary symbol is also referred to as a two-bit symbol. We represent the previous information bits that make up the two-bit symbol with a, and the latter information is represented by b. The two information bits ab in the two-bit symbol are usually arranged by Gray code (ie, reflection code). When ab is 00, the carrier phase is 0°, and when ab is 01, the carrier phase is 90°, when ab At 11 o'clock, the carrier phase is 180°, and when ab is 10, the carrier phase is 270°.

The generation of the QPSK signal is divided into a phase modulation method and a phase selection method. Since the phase modulation method is more commonly used and the actual operation is stronger, in this paper, the phase modulation method is selected. A block diagram of the composition of the QPSK signal generated by the phase modulation method is shown in FIG. In the figure, the serial/parallel converter divides the input binary sequence into two parallel bipolar sequences. Let the binary digits in the two sequences be a and b, respectively, and each pair ab is called a two-bit symbol. The bipolar a and b pulses are bi-phase modulated by the two balanced modulators for the in-phase carrier and the quadrature carrier, respectively. The two outputs of ab are superimposed to obtain a four-phase phase-shifted signal. The phase-encoding logic relationship is: when the two-bit symbol ab is 11, the output phase is 315° carrier; when ab is 01, the output phase is 225°. Carrier; when ab is 00, the output phase is 135° carrier; when ab is 10, the output phase is 45° carrier, the corresponding comparison relationship is shown in the following table.

Data versus phase

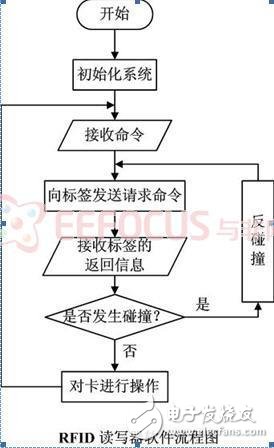

The traditional QPSK analog modulator structure generally adopts a quadrature modulation method. The implementation of the all-digital modulator still uses the quadrature modulation method, but the analog processing unit uses the algorithm of digital signal processing. QPSK uses four different carrier phases to represent digital information. Each carrier phase represents 2-bit information. In fact, there are two methods, phase selection method and quadrature modulation method. The phase selection method is divided into two methods: A and B. . In this paper, the phase selection method B is used to implement the QPSK signal, as shown in Figure 1.

Figure 1 QPSK modulation block diagram

2. MATLAB simulation of QPSK modulation

QPSK modulation MATLAB simulation related code online has many, the author of this article has written a piece of code, you can simply express the principle of modulation, here only the code is listed below, the comments are very clear, no longer repeat them. The code should be studied together with the integrated demodulation part.

Clear all;

Clc

M=4;

Ts=1;

Fc=5;

N_sample=8;% sine wave sampling points per

N_num=300; %IQ roads are 100 bits each

Dt=1/fc/N_sample;

t=0: dt: N_num*Ts-dt;

T=dt*length(t);

Noise=(1/500)*randn(1,length(t))*32767;% added noise

Py1f=zeros(1,length(t));

Py2f=zeros(1,length(t));

For PL=1:1:700% added noise intensity increase

D1=sign(randn(1,N_num));

D2=sign(randn(1,N_num));

d=[d1;d2];

D=reshape(d,1,[]); %D is the input information sequence

Gt=ones(1,fc*N_sample);

S1=sigexpand(d1,fc*N_sample);%This is a sign bit extension function, the related function is visible in the original code

S2=sigexpand(d2,fc*N_sample);

B1=conv(s1,gt);

B2=conv(s2,gt);

S1=b1(1:length(s1));

S2=b2(1:length(s2));

St_qpsk_1=s1.*round(cos(2*pi*fc*t)*32767);

St_qpsk_2=s2.*round(sin(2*pi*fc*t)*32767);

St_qpsk=st_qpsk_1+st_qpsk_2;% fixed-point quantized data

%------------------------------------------------- ----------

% power spectrum of the transmitted signal

%plot((abs(fft(st_qpsk,2048))).^2);

PGA Sockets Pin Grid Array Socket

A pin grid array, often abbreviated PGA, is a type of integrated circuit packaging. In a PGA, the package is square or rectangular, and the pins are arranged in a regular array on the underside of the package. The pins are commonly spaced 2.54 mm (0.1") apart, and may or may not cover the entire underside of the package.

PGAs are often mounted on printed circuit boards using the through hole method or inserted into a socket. PGAs allow for more pins per integrated circuit than older packages, such as dual in-line package (DIP).

PGA Sockets & Adapters

Low insertion force Pin Grid Array (PGA) Sockets and Adapters are available in a variety of RoHS Compliant insulators with hundreds of screw-machined terminal choices. Virtually any PGA footprint can be accommodated, including interstitial patterns.

PGA Sockets & Adapters Overview

Durable construction for virtually any application

Wide variety of materials, lengths, and sizes

Cost-effective method for replacing, repairing, or upgrading PGA devices

Unique options such as solder preform terminals eliminate the need for wave soldering in mixed SMT/Thru-hole applications

RoHS compliant insulators and screw-machined terminals are compatible with lead-free processing - select either Matte Tin/Gold (MG) or Gold/Gold (GG) plating

Antenk's Pin Grid Array (PGA) Sockets

Complex printed circuits are too valuable to risk direct soldering to expensive integrated circuits (ICs). Using a socket is the answer. The use of sockets offers advantages that prove cost effective and simplify board design.

Antenk's processor socket line is designed for use with Intel- and AMD-based microprocessor packages. Socket types include land grid array (LGA), micro pin grid array (mPGA), and PGA with low to zero insertion force. The mPGA and PGA sockets are designed for various microprocessor packages for notebook PCs, desktop PCs, and servers. For custom applications, the compression sockets can be configured to the specific application.

mPGA/PGA (ZIF)These sockets provide a zero insertion force (ZIF) PGA interface to the microprocessor PGA package and are attached to the PCB with surface-mount technology (SMT) soldering. PGA sockets are available in arrays up to 989 positions with single lever, screw driver, and hex wrench actuation methods.

PGA Sockets (LIF)

These sockets are primarily employed for microprocessor package test applications using through-hole solder attachment to the PCB design. The contacts are screw-machine outer sleeves with either stamped and formed or drawn inner contacts. Custom arrays are available in more than 1,000 positions.

Pin Grid Array (PGA) Sockets Type

mPGA

PGA

Eliminate hand-loading of pins, facilitate solder joint visibility, low profile component mounting or board mating.

PGA Sockets,mPGA Sockets,Integrated Circuits Socket,Pin Pga Sockets,Pga Socket Connector,PGA Adapters,Pin Grid Array Sockets,Processor Socket

ShenZhen Antenk Electronics Co,Ltd , https://www.antenkcon.com