Under Vivado, there are two ways to manage IP. One is to create an FPGA project, select the IP Catalog in the current project, generate the required IP, then the corresponding IP will be automatically added to the current project; the other is to use the Manage IP, create a separate IP project, lack In the case of the province, the name of the IP project is magaged_ip_project. Generate the required IP in this project and then add the IP to the FPGA project. Xilinx recommends using the second method, especially when there are more IPs in the design or when team design is used. As a scripting language, Tcl is used more and more widely in FPGA design. With Tcl, you can do a lot of work that can't be done by graphical interface operations, which can improve design efficiency and design automation. Vivado has good support for Tcl, specifically Tcl Shell (pure script mode) and Tcl Console (graphical interface mode) for Tcl script input and execution. This article describes how to use Tcl scripts to achieve efficient management of IP in Manage IP mode.

Manage IP features:(1) Vivado only displays the IP Catalog in the Manage IP mode, which is convenient for intuitively customizing the IP;

(2) The IP project directory is independent of the FPGA project directory and can be independently managed and facilitates IP multiplexing;

(3) Adopting an OOC (Out-of-Context) integrated method for IP, generating a corresponding DCP file and adding it to the FPGA project without re-synthesis;

The difference with ISE Core Generator:(1) ISE Core Generator different IP generation files will be in the same directory, and each IP under Vivado has a separate folder, which contains all IP related files, which provides convenience for IP multiplexing;

(2) The IP customization file generated by ISE Core Generator is .xco, and the custom file for generating IP of Vivado is .xci;

(3) The netlist file generated by the ISE Core Generator is .ngc, and the netlist file generated by Vivado is .dcp. The DCP not only contains the netlist file but also the constraint file;

(4) ISE Core Generator does not support Tcl scripts, Vivado supports Tcl scripts;

IP generation files under Vivado:(1) RTL files and constraint files for synthesis;

(2) instantiating a template file;

(3) behavioral level simulation files;

(4) The integrated netlist file DCP;

(5) Stub files for third-party integrated tools;

(6) example works;

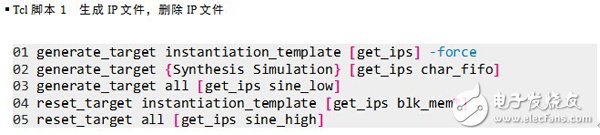

The generated file is customizable, which can be done with the generate_target command. The generated file can also be cleared by reset_target, as shown in Tcl script 1.

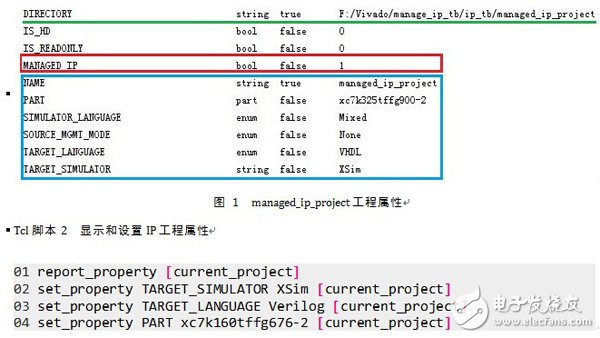

Each object under Vivado has its own properties, which can be displayed via report_property. The properties of managed_ip_project are shown in Figure 1. The green line in the figure marks the directory where the project is located; the red box MANAGED_IP attribute value is 1, indicating that the project is an IP project; the blue box is the most commonly used property when we create or modify IP project settings. The first line of the Tcl script 2 statement is used to display IP project properties, and the second to fourth line statements are used to set the simulation tool, target language, and chip model. The first parameter of the set_property command is the property name, the second parameter is the property value, and the third parameter is the object to which the property belongs.

After creating an IP project with Vivado Manage IP, you may encounter the following situations: (1) software version upgrade, such as Vivado upgrade from 2014.4 to 2014.2; (2) chip model change, for example, chip model changed from XC7K325TFFG676-2 to XC7K160TFFG676-2 (3) Some IPs in the A project are also used in the B project, and these IP parameters are configured identically. All of the above three cases can be completed by the Tcl command.

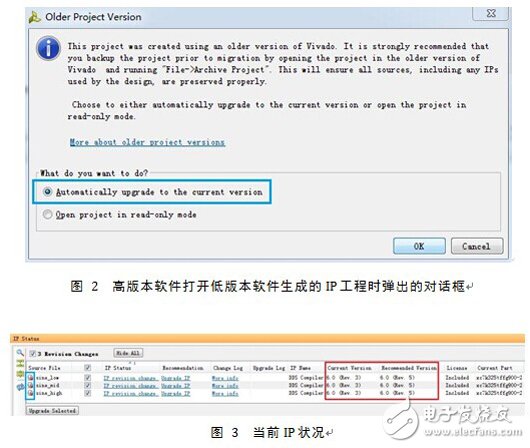

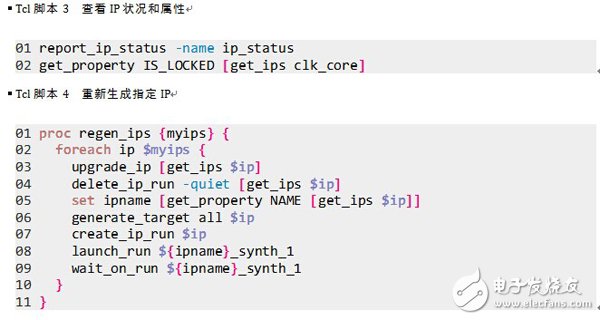

The first case: software version upgradeIf you use the IP project created by Vivado 2013.4, when the software version is upgraded to 2014.2, you need to regenerate the IP. At this point, if you open the project with Vivado 2014.2, the dialog box shown in Figure 2 will pop up. Select the option marked with the blue box in the figure to open the project, and use the report_ip_status command to display the current IP status, as shown in Figure 3.

The blue box in Figure 3 shows that the IP is locked and can be determined by the IS_LOCKED attribute of get_property; the red box shows the current version number of the IP and the new version number that is recommended to be upgraded. The corresponding Tcl script is shown in Tcl script 3. The upgrade can be selected for the locked IP, which can be upgraded by the Tcl script 4. Tcl script 4 can be embedded in Vivado as a common command for users.

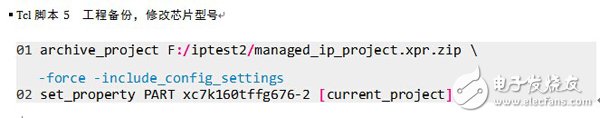

If the chip model changes, first make a backup process for the corresponding model of the old model chip, which can be done by the archive_project command; then modify the chip model. The corresponding Tcl script is shown in Tcl script 5. After completing these operations, you will find that the IP is locked. You can upgrade the IP through Tcl script 4.

In this case, the IP in the A project can be imported into the IP project of the B project, which can be done by the import_ip command, as shown in Tcl script 6. The first parameter of Import_ip is the directory where the original IP is located, and the second parameter is the new name of the IP. By default, it is the same as the original IP name. After importing, the IP can be regenerated by Tcl script 4.

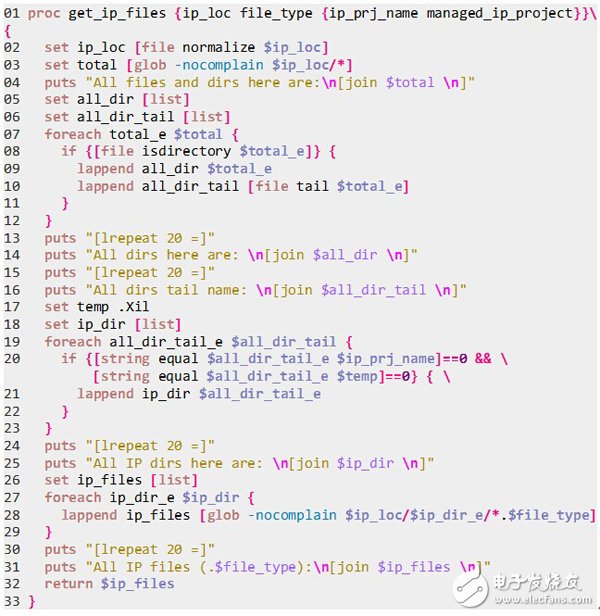

As mentioned earlier, the IP generated under Vivado has a separate file directory. When adding IP to the Vivado FPGA project, if you use the graphical interface, you need to browse to the file directory of the IP one by one, find the .xci file, and then Add to the project, if you call more IP, obviously this method is not efficient enough. At this point, you can find all IP related files by using the Tcl command shown in Tcl script 7. The file type can be xci or dcp. This command will return the full file path, such as the file path in Tcl script 6. Then add it to the current project with the add_files command.

In addition, some IPs have example projects with complete test stimuli that emulate IP to understand IP input/output timing, or to generate bit files separately. The example project can be opened with the open_example_project command, as shown in Tcl script 8.

Compared with ISE Core Generator, Vivado Manage IP manages IP more conveniently, and Vivado supports Tcl scripts. Tcl scripts can be used to manage IP more efficiently and further enhance the automation of FPGA design.

references:

[1] Xilinx. Ug896 (V2014.1) Designing with IP.

[2] Xilinx. Ug835 (V2014.2) Vivado Design Suite Tcl Command Reference Guide

Thermometers include bimetallic thermometers, pressure thermometers and marine thermometers, which are suitable for detecting and controlling the liquid level of containers in shipbuilding and other industries.Bimetallic thermometer is a field detection instrument for measuring medium and low temperature. It can directly measure the temperature of liquid steam and gas medium in the range of - 80 ℃ - + 500 ℃ in various production processes. The main element of industrial bimetallic thermometer is a multilayer metal sheet composed of two or more metal sheets, which works based on the principle that two different metals have different expansion degrees when the temperature changes. It is composed of a bimetallic sheet wound into a circular bending shape. When one end is heated and expanded, the pointer is driven to rotate, and the working instrument will display the temperature value corresponding to the thermal potential.

Pressure Type Thermometer,Metalic Protector Thermometer,Flange Bimetallic Thermometer,Glass Tube Industrial Thermometer

Taizhou Jiabo Instrument Technology Co., Ltd. , https://www.taizhoujiabo.com